On similar lines a bad floorplan can create all kind issues in the design. A core utilization of 08 means that 80 of the area is available for placement of cells whereas 20 is left free for routing.

Floorplan Control Parameters Vlsi Basics And Interview Questions Lmr

If there are then add this also X um Y um.

. Of Electronics and communication Engineering REVA University Bengaluru India----------Abstract Physical Design implementation means the. Core U tilizationstandard cell area macro cells areapad area total core area. The utilization will be shown in your command shell window.

Generates more accurate core and module sizes. What is core limited and pad limited design. Posted by Akshay at 2116.

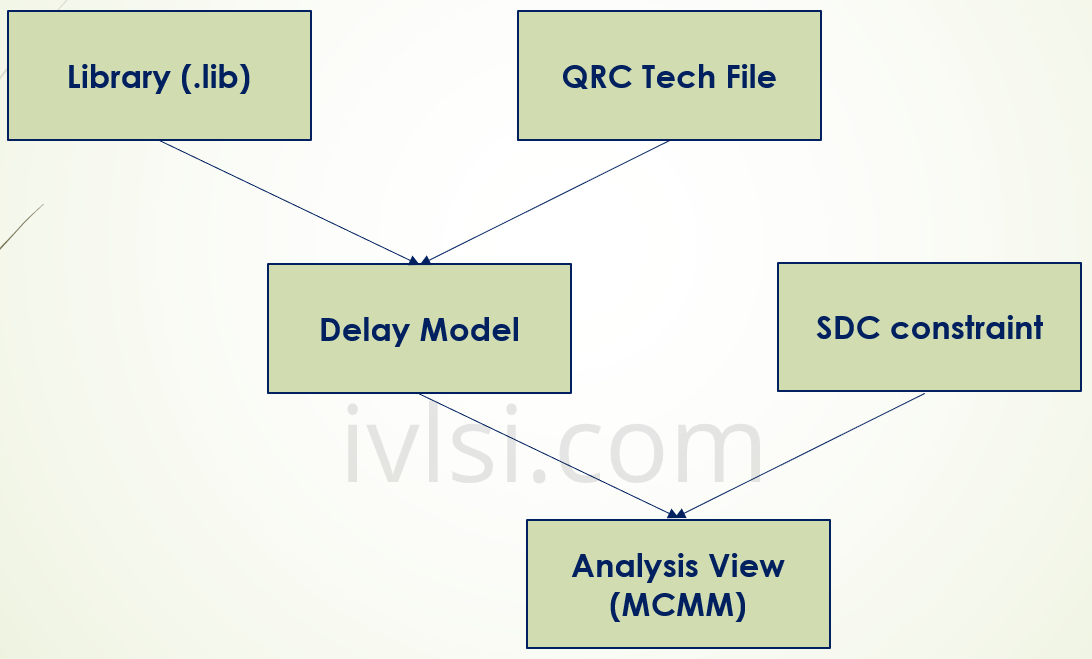

Libraries In Physical Design. Of Electronics and communication Engineering REVA University Bengaluru India----------Abstract Physical Design implementation means the. A good floorplan can be make implementation process place cts route timing closure cake walk.

Core to IO boundary. By Jaya Patel Atul Kumar eInfochips - An Arrow company Abstract. You can specify a.

The number is calculated as a ratio of the total cell area for hard macros and standard cells or soft macro cells to the core area. Core utilization percentage indicates the amount of core area used for cell placement. When designer is done with the floorplan the next step is to run placement and optimization after completion of placement and optimization designer would analyse the.

Physical and chemical phenomena are affected from the nano- andor. The core idea of multiscale modelling is not in the effusive complication of materials related. Thread s per core.

How is macro placement done in floor planning. In a VLSI design floorplan is the crucial stage in which chip area size and shape of the chip can be determinedFloorplan is iterative process. This number represents the Logical CPU count under each Core.

70 of the core. Can macro be placed between core and die boundary or in IO pad. Rcr Row area Core area H x V.

Floorplanning Die Size Size Utilization Metal Stack-up Choosing the die size initial standard cell utilization and metallization scheme involves several design tradeoffs Schedule Cost Performance Larger die Easier to route less congestion lower cap decrease signalpower integrity related problems faster design problems cycle Higher cost higher. A value of 10 leaves no routing channel space. Core Size standard cell areastandard cell utilization macro area halo.

Physical Design Implementation of Single Core 32 Bit RISC Processor on 28nm Technology Feroz Ahmed Choudhary1 Amay Shiva Naik2 Dr. Of standard cells one standard cell area Alternatively this can be directly obtained from the DC area report. Physical Design Flow IIPlacement.

After you have done floorplanning ie. What is placement. Cadence Internal Use Only Quiz.

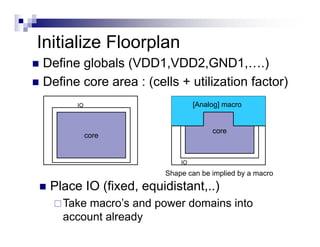

Creating and developing a physical model of the design in the form of an initial optimized layout Because floorplanning significantly affects circuit timing and performance especially for complex hierarchical designs the quality of your floorplan directly affects the quality of your final design Calculation of Core Die size and Aspect Ratio. Created the core area placed the macros and decided the power network structure of your design it is time to let the tool to do standard cell placement. A processor contains corethreads etc.

ASIC Physical Design Standard-Cell Design Flow Using the Cadence Innovus Digital Implementation System. What are the guidelines for macro placement. Core to IO clearence.

Given the design at right with a single buffer that is relatively tiny and a large macro that occupies half of the. The smaller the number the more space is left for routing. Core Utilization defines the area occupied by standard cell macros and blockages.

Design Construction and Utilization of Physical Vapor Deposition Systems for Medical Sensor Fabrication Nicholas Sayre Portland State University nsayrepdxedu Erik J. Floorplan is one the critical important step in Physical design. Core size Standard cell area Utilization Assuming there are no hard macros.

Core utilization-Utilization will define the area occupied by the standard cells macros and other cellsIf core utilization is 08 80 that means 80 of the core area is used for placing the standard cells macros and other cells and the remaining 20 is used for routing purposes. Quality of your Chip Design implementation depends on how good is the Floorplan. To see the core utilization click button in the toolbar and drag and make a rectangle containing the core region.

Core utilization standard cell area macro cells area total core area. We define Core Size By or Die Size By where core size by is defined by aspect ratio HeightWidth and core utilization or dimension where we define height and width of core. If the name of a cell is not present in the current design it will consider as physical only cells.

Core utilization standard cell area macro cells area total core area A core utilization of 08 means that 80 of the area is available for placement of cells whereas 20 is left free for routing. Total standard cell area no. If core utilization of 08 means that 80 of the area is available for placement of cells whereas 20 is left for routing.

Leaves space for. What is core utilization. These cells are not present in the design netlist.

A core utilization of 08 for example means that 80 of the core area is used for cell placement and 20 percent is available for routing. Why do you need to do it before placement. Core utilization Core utilization standard cell area macro cells area total core area A core utilization of 08 means that 80 of the area is available for placement of cells whereas 20 is left free for routing.

It indicates the amount of channel space to provide for routing between the cell rows. Core s per socket. It will be about 221 in this example.

Core utilization and standard cell utilization gops over 13 years ago what is the difference between core utilization and standard cell utilizationSome body. What is total chip utilization. Cell Utilization Q.

The tool determines the location of each of the components in digital design standard cell instantiations on the. Core utilization leaves space for routing. 4 November 12 2008 Cadence Confidential.

They do not appear on timing paths reportsthey are typically invented for finishing the chip. Performance better utilization and leads to more cost effective solutions. In the above example there are 4 cores under 1 processor.

Core utilization allowed eg07 ie70 Calculations. Sánchez Portland State University esanchezpdxedu Joe Kowalski Portland State University Let us know how access to this document benefits you. Core UtilizationCu Standard Cell areaRow area Channel area Row to Core Ratio Rcr.

This number represents the count of the physical core CPU to which the hardware thread logical CPU belongs. ASIC Physical Design Standard Cell can also do full custom layout. Rajashekhar C Biradar3 123Dept.

What Is Floorplanning Vlsi Physical Design For Freshers

What Is Floorplanning Vlsi Physical Design For Freshers

What Is Floorplanning Vlsi Physical Design For Freshers

Floorplan Control Parameters Vlsi Basics And Interview Questions Lmr

What Is Floorplanning Vlsi Physical Design For Freshers

0 comments

Post a Comment